zedboard-用户自定义IP核设计(pwm发生器)

日期:2014-05-16 浏览次数:20423 次

1:实验说明:

对于Zedboard的用户自定义的IP核有两种可行的方案:

一:通过EMIO交换数据(GPIO,SPI),这个其实就是将PL的IP核看作系统的外设,在数据交互性能和效率上都有很大的缺陷。(不常用)

二:利用向导来制作满足AXI协议的IP核,向导自动生成总线相关的代码,做好地址译码逻辑,读写控制逻辑,并在用户工作区生成一些寄存器。我们写的PL逻辑通过读写这些寄存器和PS交互。这也是常用的方法。

Zedboard也有一些自己做好了的IP core,实验八就是用的自带的IP core。

本实验就是采用第二种方法,制作一个简单的PWM发生器。在PL端开发了这个IP核以后,先在裸跑的程序里面调用这个IP core,测试我们的逻辑有没有实现,这个和之前做的实验没有什么区别(zedboard--zynq使用自带外设IP让ARM PS访问FPGA(八),只不过这里是我们自己写的IP core)

PWM发生器内部只有两个寄存器,一个是调节周期的周期寄存器,另一个是调节占空比的占空比寄存器,其中周期寄存器的最高位是状态位,控制PWM波最后是否产生。

2:具体步骤

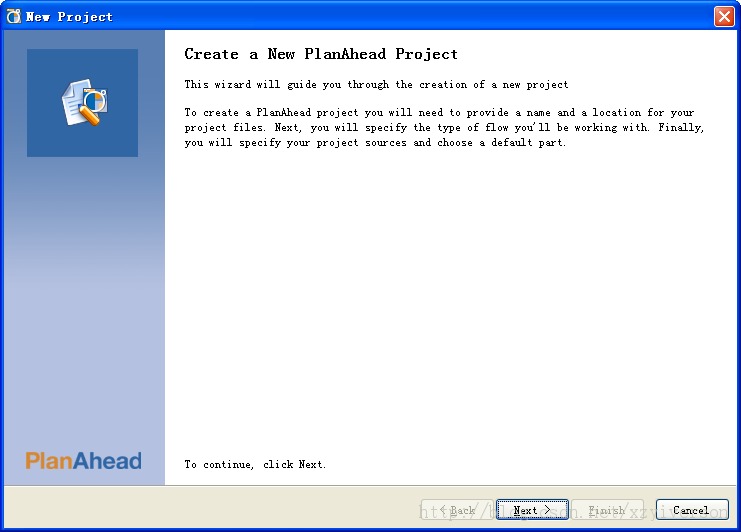

启动PlanAhead,创建工程,Next,图1

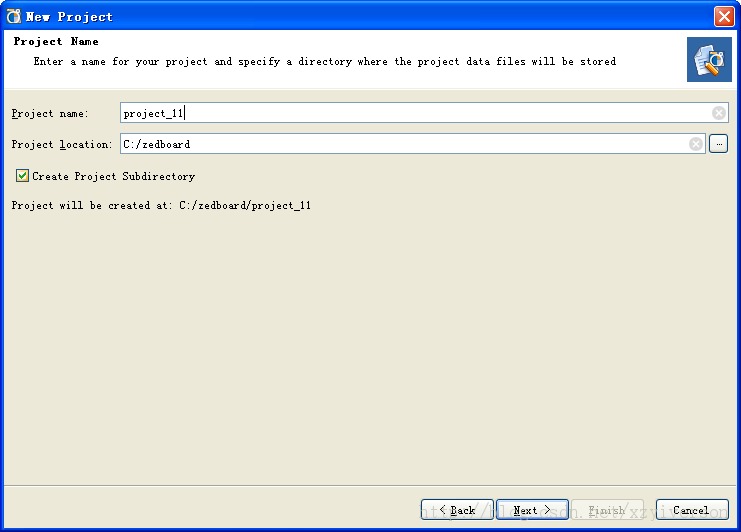

输入工程名project_10,Next,图2

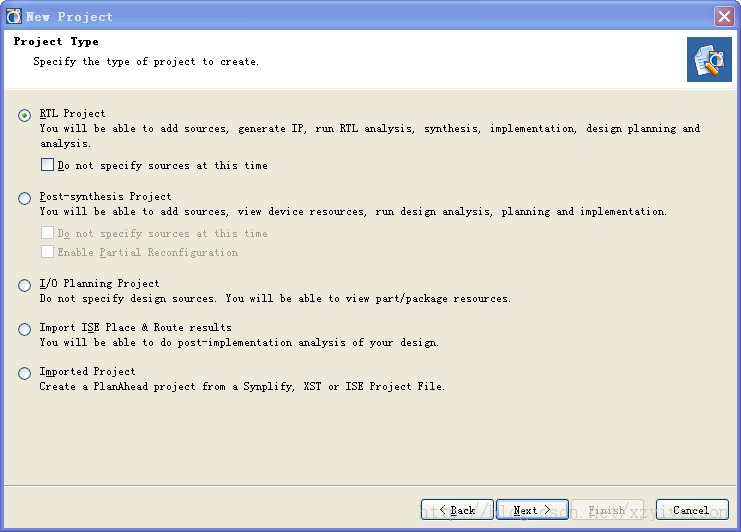

Next,RTL工程 图3

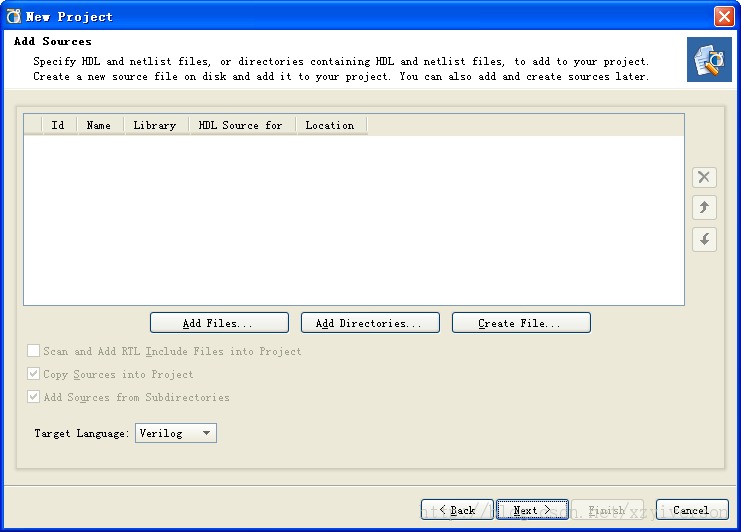

一路Next,不添加任何文件 图4

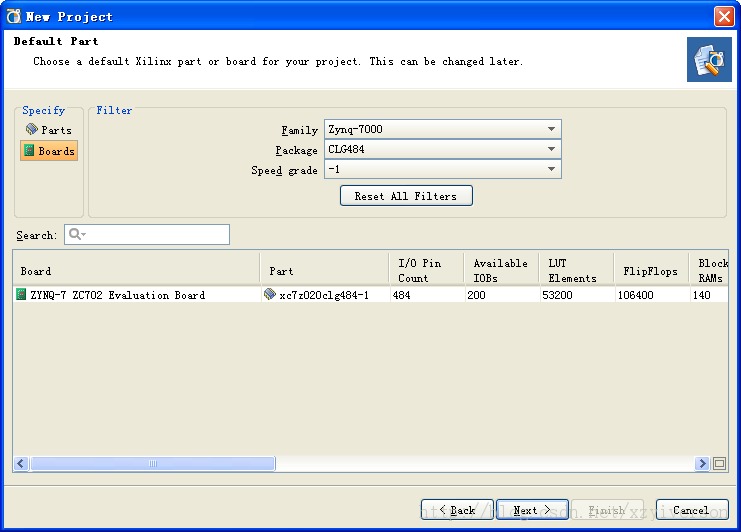

选择board 图5

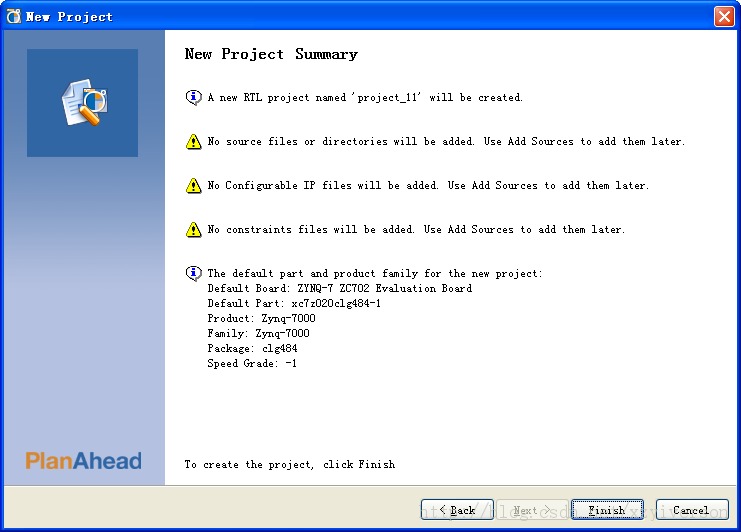

完成工程 图6

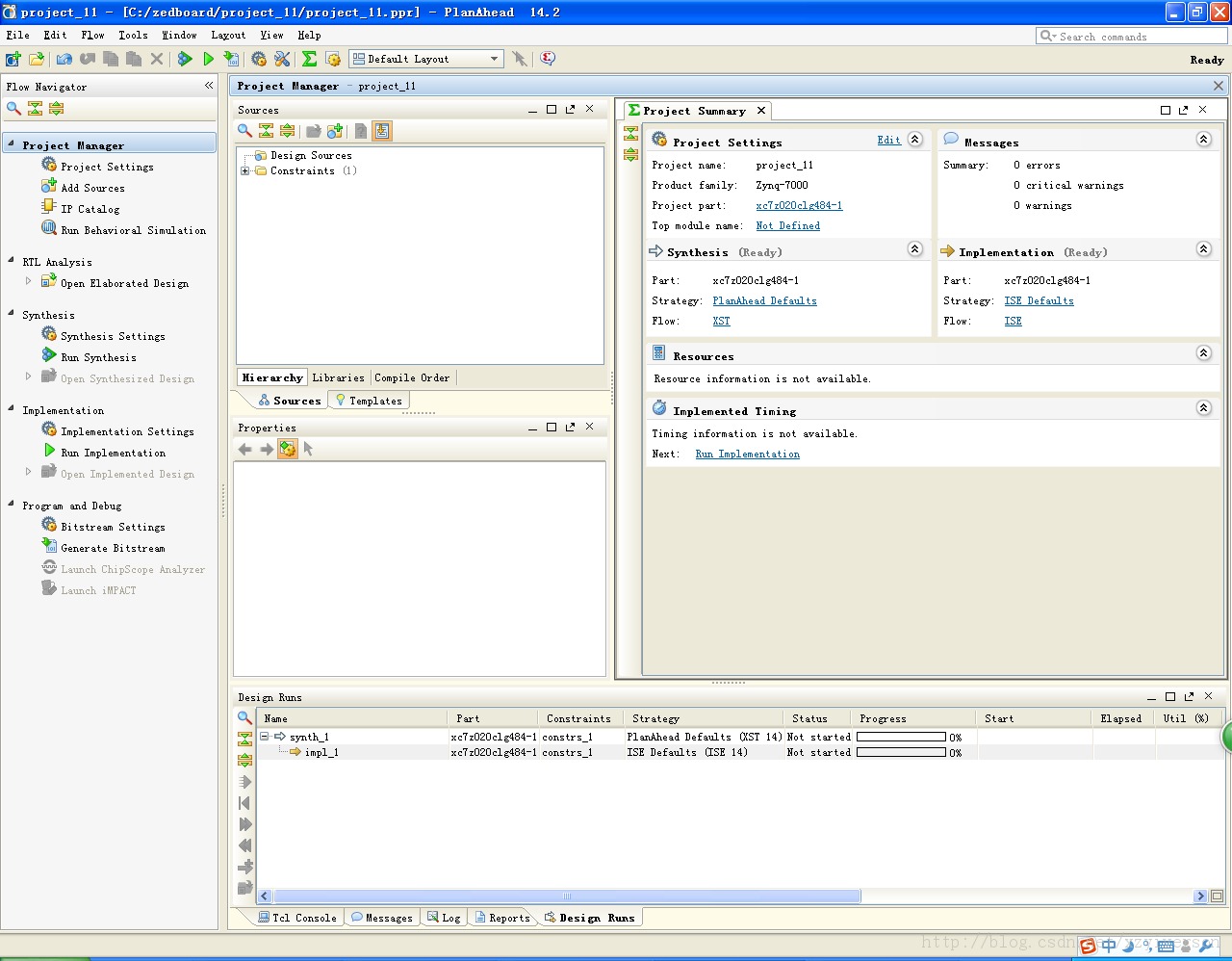

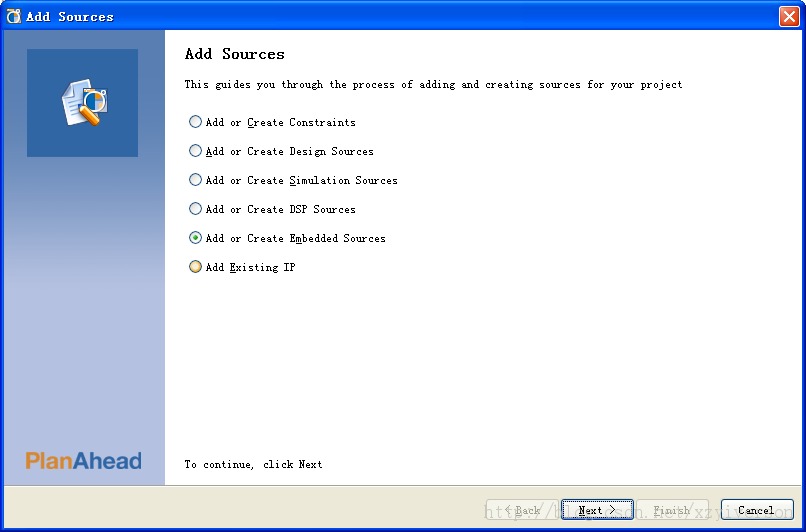

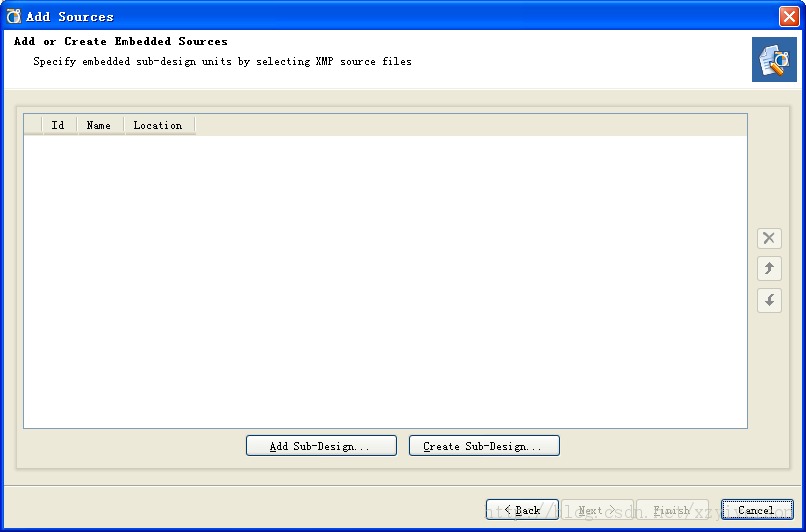

PlanAhead进入工作视图,在Project Manager中单击那个有+的图标(addsources),出现下图,选择Embedded Sources 图7,图8

Next 选着Create Sub-Design。 图9

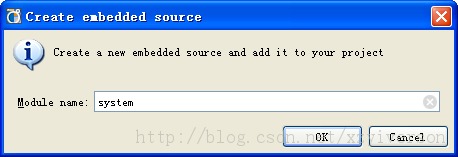

输入名称,这里为system 图10

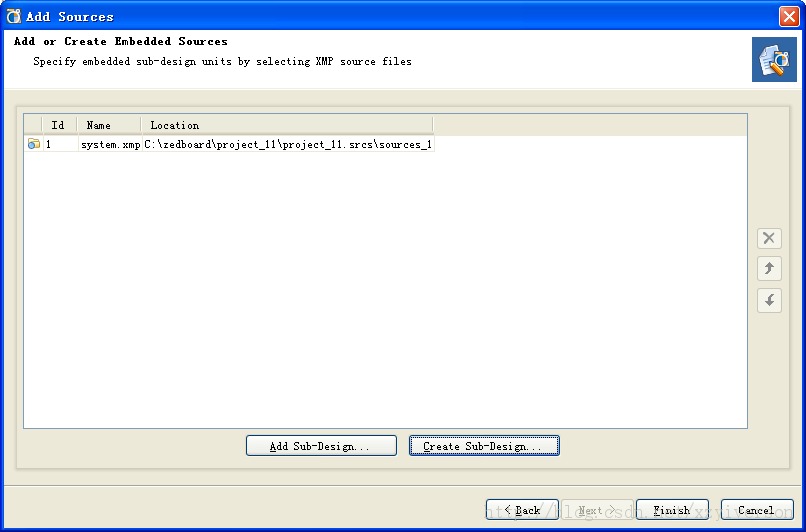

点击finish 图11

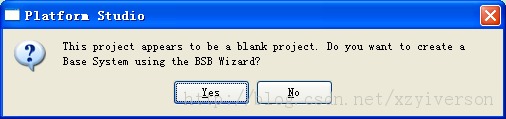

进入了XPS,提示所建立的一个zynq工程,提示是否建立bsb Wizard,选择yes 图12

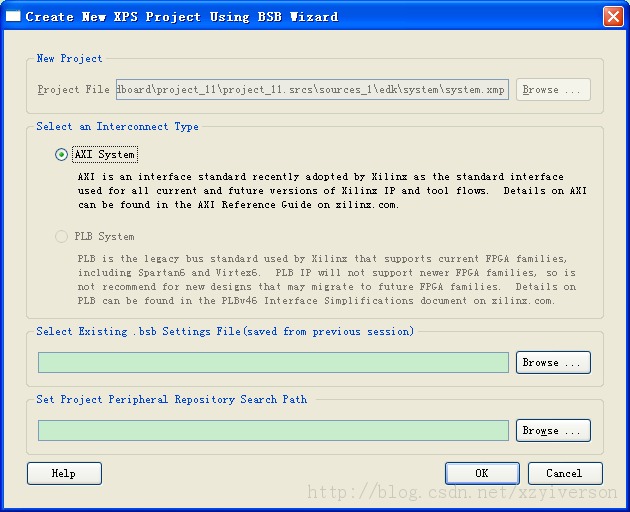

出现下图 图13

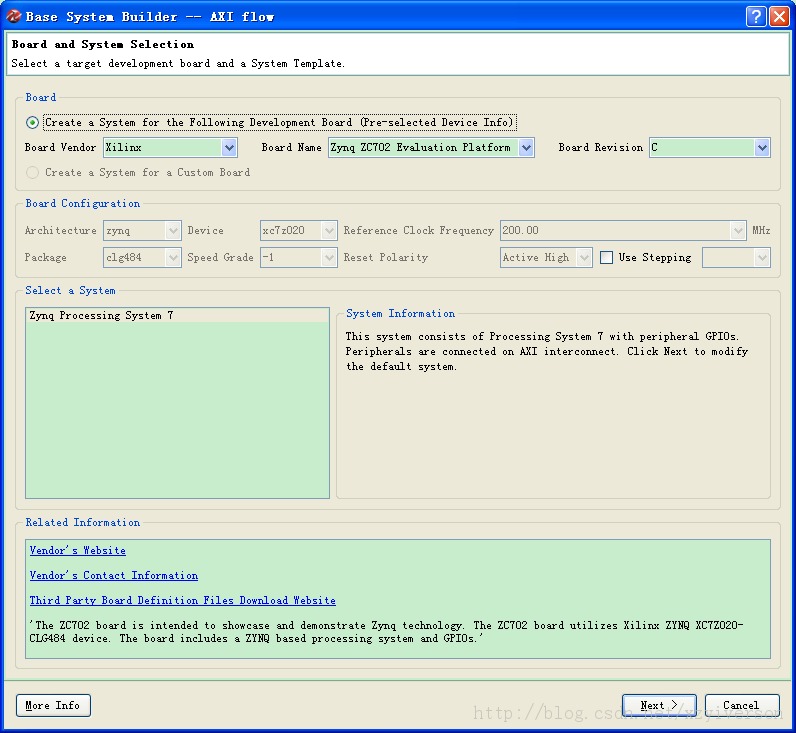

点击ok 出现 图14

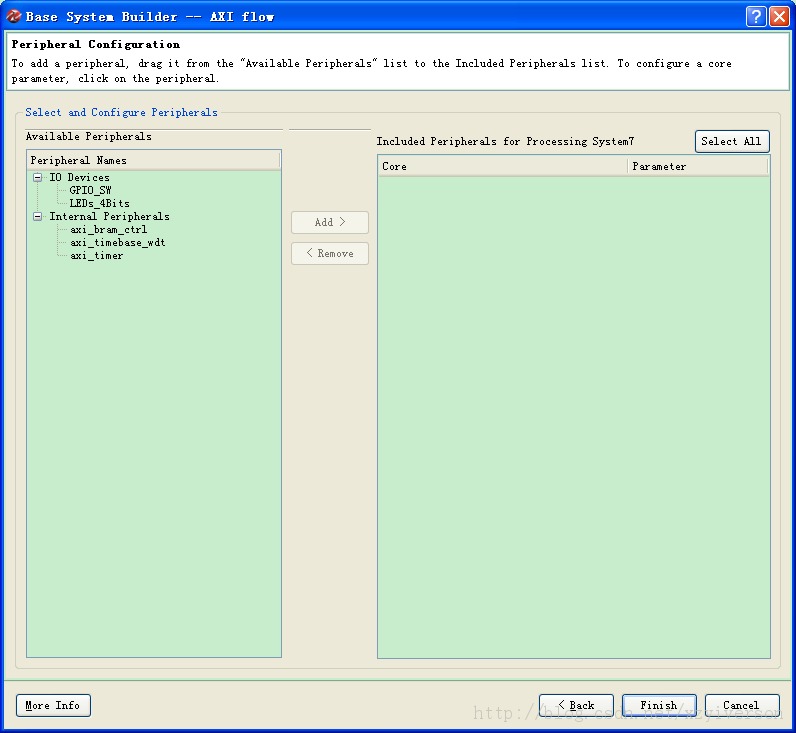

选择next 这里不要大意,一定要把右侧的两个东西来remove掉,我当时就是卡在这里。,remove后出现这样的图 图15

Finish,点击finish就可以了,然后进入zynq的配置界面,Diligent公司做好了一个配置方案,可以到网上下载到配置文件。

如图16 17 18